## **Mechatronics and Microcomputers**

Stipendium Hungaricum 2018/2019 Autumn Semester Szilárd Aradi, PhD

20/11/2018

Mechatronics and Microcontrollers

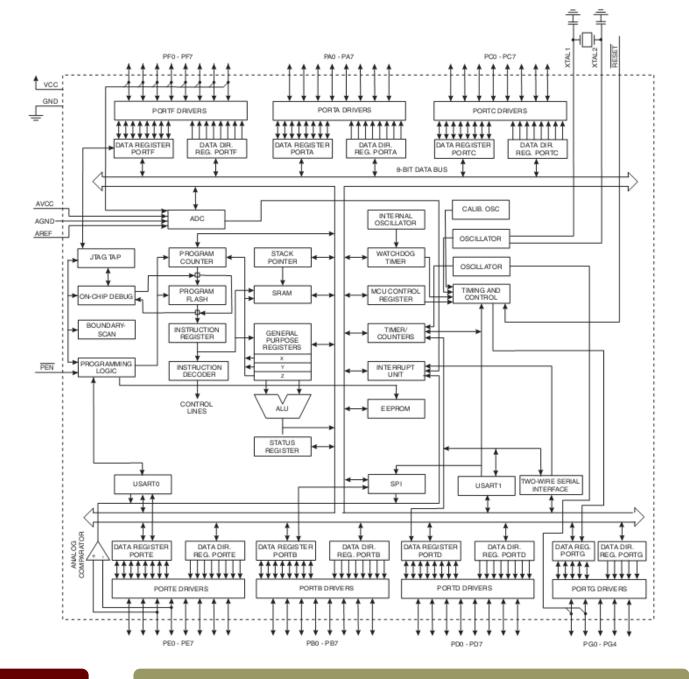

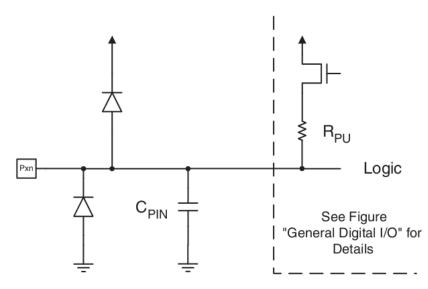

# I/O ports

- Data Direction Register (DDRx)

- 0: input, 1: output

- The direction of one port pin can be changed without unintentionally changing the direction of any other pin

- Port Register (PORTx)

- If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated.

- If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one).

- Pin Register (PINx)

- Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register bit.

| DDxn | PORTxn | PUD<br>(in SFIOR) | I/O    | Pull-up | Comment                                     |

|------|--------|-------------------|--------|---------|---------------------------------------------|

| 0    | 0      | Х                 | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 0                 | Input  | Yes     | Pxn will source current if ext. pulled low. |

| 0    | 1      | 1                 | Input  | No      | Tri-state (Hi-Z)                            |

| 1    | 0      | Х                 | Output | No      | Output Low (Sink)                           |

| 1    | 1      | Х                 | Output | No      | Output High (Source)                        |

# Timer/Counter

- Two 8-bit Timer/Counters and two expanded 16-bit Timer/Counters

- Separate Prescalers

- Compare Modes with auto reloading

- Capture Mode

- Two 8-bit PWM Channels

- 6 PWM Channels with Programmable Resolution from 2 to 16 Bits

- Different Interrupt Sources

- Overflow

- Output Compare

- Input Capture

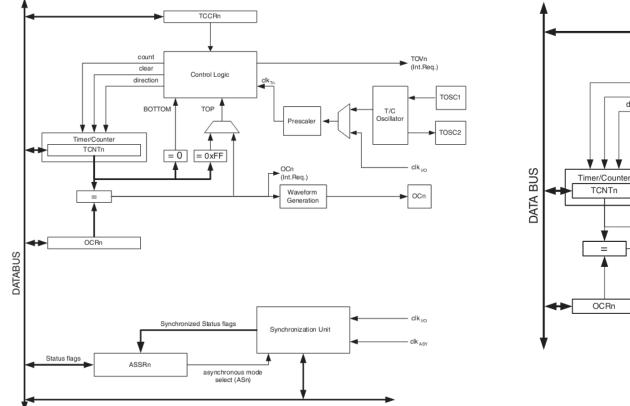

#### 8-bit Timer/Counter I.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### Timer/Counter0

Timer/Counter2

## 8-bites Timer/Counter II.

- Normal Mode

- The simplest mode of operation is the normal mode. In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (0xFF) and then restarts from the bottom (0x00). In normal operation the Timer/Counter overflow flag (TOV0) will be set in the same timer clock cycle as the TCNT0 becomes zero.

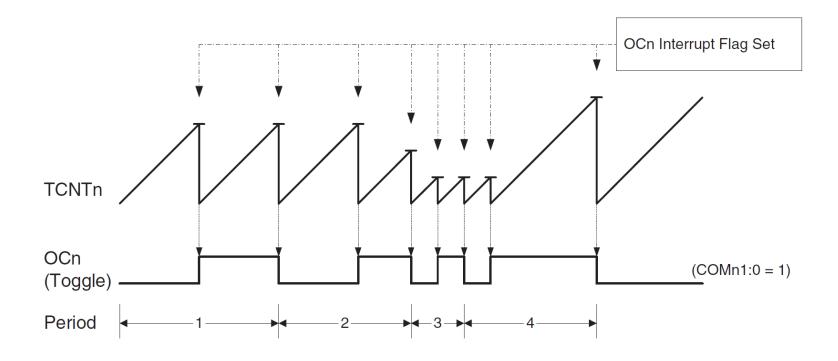

- Clear Timer on Compare Match (CTC) Mode

- In Clear Timer on Compare or CTC mode, the OCR0 Register is used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT0) matches the OCR0. The OCR0 defines the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency.

- An interrupt can be generated each time the counter value reaches the TOP value by using the OCF0 flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value.

$$f_{OCn} = \frac{f_{\mathsf{clk\_I/O}}}{2 \cdot N \cdot (1 + OCRn)}$$

# CTC Mode, Timing Diagram

## 8-bit Timer/Counter III.

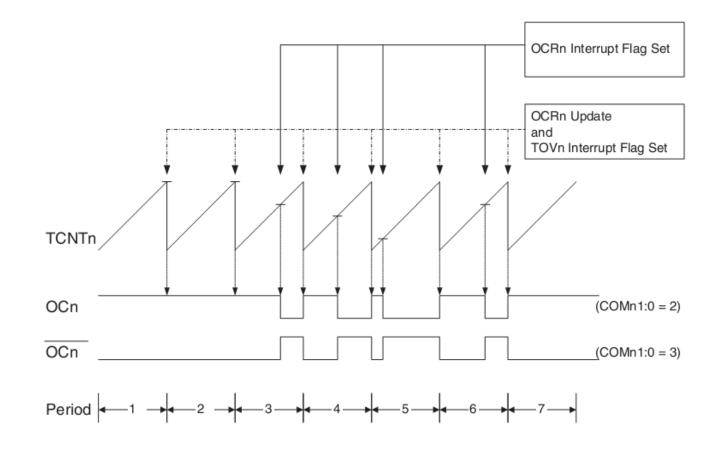

- Fast PWM Mode

- The fast Pulse Width Modulation or fast PWM mode provides a high frequency PWM waveform generation option.

- This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors).

- The counter counts from 0x00 to 0xFF then restarts from 0x00. In non-inverting Compare Output mode, the output compare (OC0) is cleared on the compare match between TCNT0 and OCR0, and set at 0x00. In inverting Compare Output mode, the output is set on compare match and cleared at 0x00.  $f_{OCnPWM} = \frac{f_{Clk\_1/0}}{N_{1}\cdot 256}$

#### Fast PWM Mode, Timing Diagram

# 8-bit Timer/Counter IV.

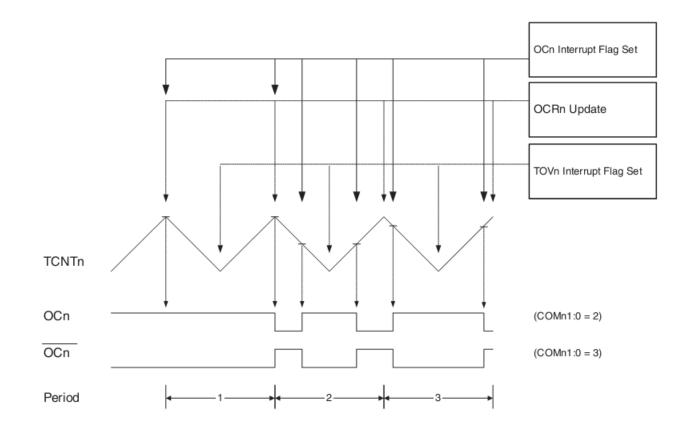

- Phase Correct PWM Mode

- The phase correct PWM mode provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to MAX and then from MAX to BOTTOM. In noninverting

- Compare Output mode, the output compare (OC0) is cleared on the compare match between TCNT0 and OCR0 while counting up, and set on the compare match while downcounting. In inverting Output Compare mode, the operation is inverted.

- The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.  $f_{OCnPCPWM} = \frac{f_{clk\_VO}}{N \cdot 510}$

### Phase Correct PWM Mode, Timing Diagram

### 8-bit Timer/Counter VI.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

| • | Time          | r/0  | Cou   | nte   | er C  | ont   | rol  | Re   | gist | ter ( | (TCCR0) |

|---|---------------|------|-------|-------|-------|-------|------|------|------|-------|---------|

|   | Bit           | 7    | 6     | 5     | 4     | 3     | 2    | 1    | 0    |       |         |

|   |               | FOC0 | WGM00 | COM01 | COM00 | WGM01 | CS02 | CS01 | CS00 | TCCR0 |         |

|   | Read/Write    | W    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | •     |         |

|   | Initial Value | 0    | 0     | 0     | 0     | 0     | 0    | 0    | 0    |       |         |

- Force Output Compare (FOC0) bit

- The FOC0 bit is only active when the WGM bits specify a non-PWM mode. When writing a logical one to the FOC0 bit, the OC0 output is changed according to its COM01:0 bits setting.

#### • Waveform Generation Mode (WGM0 1:0) bits

| Mode | WGM01 <sup>(1)</sup><br>(CTC0) | WGM00 <sup>(1)</sup><br>(PWM0) | Timer/Counter<br>Mode of Operation | тор  | Update of<br>OCR0 at | TOV0 Flag<br>Set on |

|------|--------------------------------|--------------------------------|------------------------------------|------|----------------------|---------------------|

| 0    | 0                              | 0                              | Normal                             | 0xFF | Immediate            | MAX                 |

| 1    | 0                              | 1                              | PWM, Phase<br>Correct              | 0xFF | TOP                  | BOTTOM              |

| 2    | 1                              | 0                              | СТС                                | OCR0 | Immediate            | MAX                 |

| 3    | 1                              | 1                              | Fast PWM                           | 0xFF | BOTTOM               | MAX                 |

### 8-bit Timer/Counter VII.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

| • | Time       | r/0  | Cou   | nte   | r C   | ont   | rol  | Re   | gist | ter (TCCR0) |

|---|------------|------|-------|-------|-------|-------|------|------|------|-------------|

|   | Bit        | 7    | 6     | 5     | 4     | 3     | 2    | 1    | 0    |             |

|   |            | FOC0 | WGM00 | COM01 | COM00 | WGM01 | CS02 | CS01 | CS00 | TCCR0       |

|   |            |      |       |       |       |       |      |      |      |             |

|   | Read/Write | W    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  |             |

• Compare Match Output Mode (COM0 1:0) bit

#### Normal Mode

| COM01 | COM00 | Description                              |  |  |  |

|-------|-------|------------------------------------------|--|--|--|

| 0     | 0     | Normal port operation, OC0 disconnected. |  |  |  |

| 0     | 1     | Toggle OC0 on compare match              |  |  |  |

| 1     | 0     | Clear OC0 on compare match               |  |  |  |

| 1     | 1     | Set OC0 on compare match                 |  |  |  |

#### Fast PWM Mode

| COM01 | COM00 | Description                                                         |  |  |  |  |  |

|-------|-------|---------------------------------------------------------------------|--|--|--|--|--|

| 0     | 0     | Normal port operation, OC0 disconnected.                            |  |  |  |  |  |

| 0     | 1     | Reserved                                                            |  |  |  |  |  |

| 1     | 0     | Clear OC0 on compare match, set OC0 at BOTTOM, (non-inverting mode) |  |  |  |  |  |

| 1     | 1     | Set OC0 on compare match, clear OC0 at BOTTOM, (inverting mode)     |  |  |  |  |  |

#### Phase Correct PWM Mode

| COM01 | COM00 | Description                                                                              |

|-------|-------|------------------------------------------------------------------------------------------|

| 0     | 0     | Normal port operation, OC0 disconnected.                                                 |

| 0     | 1     | Reserved                                                                                 |

| 1     | 0     | Clear OC0 on compare match when up-counting. Set OC0 on compare match when downcounting. |

| 1     | 1     | Set OC0 on compare match when up-counting. Clear OC0 on compare match when downcounting. |

#### 20/11/2018

#### Mechatronics and Microcontrollers

### 8-bit Timer/Counter VIII.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

| • | Timer | C/C | our | nter | Сс | ontr | ol | Reg | ister | (TCCR0) |

|---|-------|-----|-----|------|----|------|----|-----|-------|---------|

|   |       |     | 6   |      |    |      |    | 4   | 0     | ` '     |

| DI            | /    | 0     | 5     | 4     | 3     | 2    | 1    | 0    | _     |

|---------------|------|-------|-------|-------|-------|------|------|------|-------|

|               | FOC0 | WGM00 | COM01 | COM00 | WGM01 | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write    | W    | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | •     |

| Initial Value | 0    | 0     | 0     | 0     | 0     | 0    | 0    | 0    |       |

• Clock Select (CS0 2:0) bit

| CS02 | CS01 | CS00 | Description                               |  |

|------|------|------|-------------------------------------------|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped)   |  |

| 0    | 0    | 1    | clk <sub>T0S</sub> /(No prescaling)       |  |

| 0    | 1    | 0    | clk <sub>T0S</sub> /8 (From prescaler)    |  |

| 0    | 1    | 1    | clk <sub>T0S</sub> /32 (From prescaler)   |  |

| 1    | 0    | 0    | clk <sub>T0S</sub> /64 (From prescaler)   |  |

| 1    | 0    | 1    | clk <sub>T0S</sub> /128 (From prescaler)  |  |

| 1    | 1    | 0    | clk <sub>T0S</sub> /256 (From prescaler)  |  |

| 1    | 1    | 1    | clk <sub>TOS</sub> /1024 (From prescaler) |  |

## 8-bit Timer/Counter IX.

- Timer/Counter Register (TCNT0)

- 8-bit counter register. It is directly readable and writable. But modifying the counter (TCNT0) while the counter is running, introduces a risk of missing a compare match between TCNT0 and the OCR0 Register.

- Output Compare Register (OCR0)

- The Output Compare Register contains an 8-bit value that is continuously compared with the counter value (TCNT0). A match can be used to generate an output compare interrupt, or to generate a waveform output on the OC0 pin.

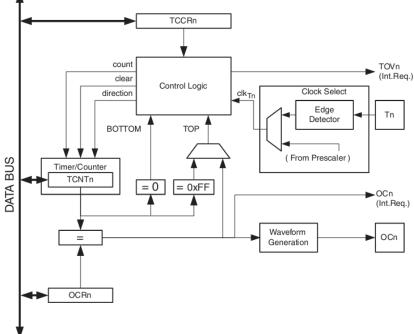

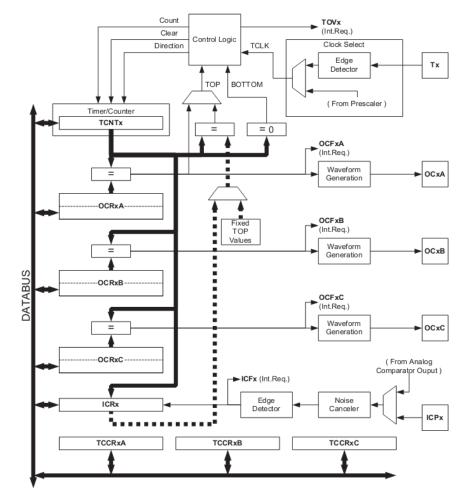

# 16-bit Timer/Counter I.

- Main differences

- Three Output Compare module

- Input Capture module

- Phase and Frequency Correct PWM

- 16-bit registers that can be accessed by the AVR CPU via the 8-bit data bus.

- The 16-bit register must be byte accessed using two read or write operations.

- Each 16-bit timer has a single 8-bit register for temporary storing of the high byte of the 16-bit access. The same Temporary Register is shared between all 16-bit registers within each 16-bit timer.

- Accessing the low byte triggers the 16-bit read or write operation.

#### 16-bit Timer/Counter II.

### 16-bit Timer/Counter III.

| Budapesti     | i Műszaki és | Gazdaságtu | ıdományi Eg | yetem Közl | lekedésauto | matikai Tan | szék 🧲 |       |        |

|---------------|--------------|------------|-------------|------------|-------------|-------------|--------|-------|--------|

| Bit           | 7            | 6          | 5           | 4          | 3           | 2           | 1      | 0     |        |

|               | COM1A1       | COM1A0     | COM1B1      | COM1B0     | COM1C1      | COM1C0      | WGM11  | WGM10 | TCCR1A |

| Read/Write    | R/W          | R/W        | R/W         | R/W        | R/W         | R/W         | R/W    | R/W   | •      |

| Initial Value | 0            | 0          | 0           | 0          | 0           | 0           | 0      | 0     |        |

| Bit           | 7            | 6          | 5           | 4          | 3           | 2           | 1      | 0     |        |

|               | COM3A1       | COM3A0     | COM3B1      | COM3B0     | COM3C1      | COM3C0      | WGM31  | WGM30 | TCCR3A |

| Read/Write    | R/W          | R/W        | R/W         | R/W        | R/W         | R/W         | R/W    | R/W   | -      |

| Initial Value | 0            | 0          | 0           | 0          | 0           | 0           | 0      | 0     |        |

| Bit           | 7            | 6          | 5           | 4          | 3           | 2           | 1      | 0     |        |

|               | ICNC1        | ICES1      | -           | WGM13      | WGM12       | CS12        | CS11   | CS10  | TCCR1B |

| Read/Write    | R/W          | R/W        | R           | R/W        | R/W         | R/W         | R/W    | R/W   |        |

| Initial Value | 0            | 0          | 0           | 0          | 0           | 0           | 0      | 0     |        |

| Bit           | 7            | 6          | 5           | 4          | 3           | 2           | 1      | 0     |        |

|               | ICNC3        | ICES3      | -           | WGM33      | WGM32       | CS32        | CS31   | CS30  | TCCR3B |

| Read/Write    | R/W          | R/W        | R           | R/W        | R/W         | R/W         | R/W    | R/W   |        |

| Initial Value | 0            | 0          | 0           | 0          | 0           | 0           | 0      | 0     |        |

| Bit           | 7            | 6          | 5           | 4          | 3           | 2           | 1      | 0     |        |

|               | FOC1A        | FOC1B      | FOC1C       | -          | -           | -           | -      | -     | TCCR1C |

| Read/Write    | W            | W          | W           | R          | R           | R           | R      | R     |        |

| Initial Value | 0            | 0          | 0           | 0          | 0           | 0           | 0      | 0     |        |

| Bit           | 7            | 6          | 5           | 4          | 3           | 2           | 1      | 0     | 1      |

|               | FOC3A        | FOC3B      | FOC3C       | -          | -           | -           | -      | -     | TCCR3C |

| Read/Write    | W            | W          | W           | R          | R           | R           | R      | R     |        |

| Initial Value | 0            | 0          | 0           | 0          | 0           | 0           | 0      | 0     |        |

### 16-bit Timer/Counter IV.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### Compare Match Output Mode (A, B, C channel)

#### Normal Mode

| COMnA1/COMnB1/<br>COMnC1 | COMnA0/COMnB0/<br>COMnC0 | Description                                                      |

|--------------------------|--------------------------|------------------------------------------------------------------|

| 0                        | 0                        | Normal port operation, OCnA/OCnB/OCnC disconnected.              |

| 0                        | 1                        | Toggle OCnA/OCnB/OCnC on compare match.                          |

| 1                        | 0                        | Clear OCnA/OCnB/OCnC on compare match (set output to low level). |

| 1                        | 1                        | Set OCnA/OCnB/OCnC on compare match (set output to high level).  |

Fast PWM Mode

| COMnA1/COMnB1/<br>COMnC1 | COMnA0/COMnB0/<br>COMnC0 | Description                                                                                                                                                                                 |

|--------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                        | 0                        | Normal port operation, OCnA/OCnB/OCnC disconnected.                                                                                                                                         |

| 0                        | 1                        | WGMn3:0 = 15: Toggle OCnA on Compare<br>Match, OCnB/OCnC disconnected (normal<br>port operation).<br>For all other WGMn settings, normal port<br>operation, OCnA/OCnB/OCnC<br>disconnected. |

| 1                        | 0                        | Clear OCnA/OCnB/OCnC on compare<br>match, set OCnA/OCnB/OCnC at BOTTOM,<br>(non-inverting mode)                                                                                             |

| 1                        | 1                        | Set OCnA/OCnB/OCnC on compare match,<br>clear OCnA/OCnB/OCnC at BOTTOM,<br>(inverting mode)                                                                                                 |

#### Phase Correct (and Fr. Correct) PWM Mode

| COMnA1/COMnB1/<br>COMnC1 | COMnA0/COMnB0/<br>COMnC0 | Description                                                                                                                                                                                      |  |  |  |  |

|--------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                        | 0                        | Normal port operation, OCnA/OCnB/OCnC disconnected.                                                                                                                                              |  |  |  |  |

| 0                        | 1                        | WGMn3:0 = 9 or 11: Toggle OCnA on<br>Compare Match, OCnB/OCnC disconnected<br>(normal port operation).<br>For all other WGMn settings, normal port<br>operation, OCnA/OCnB/OCnC<br>disconnected. |  |  |  |  |

| 1                        | 0                        | Clear OCnA/OCnB/OCnC on compare<br>match when up-counting. Set<br>OCnA/OCnB/OCnC on compare match<br>when downcounting.                                                                          |  |  |  |  |

| 1                        | 1                        | Set OCnA/OCnB/OCnC on compare match<br>when up-counting. Clear<br>OCnA/OCnB/OCnC on compare match<br>when downcounting.                                                                          |  |  |  |  |

#### Mechatronics and Microcontrollers

## 16-bit Timer/Counter V.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### Waveform Generation Mode

| Mode | WGMn3 | WGMn2<br>(CTCn) | WGMn1<br>(PWMn1) | WGMn0<br>(PWMn0) | Timer/Counter Mode of Operation <sup>(1)</sup> | ТОР    | Update of<br>OCRnx at | TOVn Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|------------------------------------------------|--------|-----------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                                         | 0xFFFF | Immediate             | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit                      | 0x00FF | TOP                   | BOTTOM              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit                      | 0x01FF | TOP                   | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit                     | 0x03FF | TOP                   | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | СТС                                            | OCRnA  | Immediate             | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                                | 0x00FF | BOTTOM                | TOP                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                                | 0x01FF | BOTTOM                | TOP                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                               | 0x03FF | BOTTOM                | TOP                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct            | ICRn   | воттом                | воттом              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct            | OCRnA  | BOTTOM                | воттом              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                             | ICRn   | TOP                   | BOTTOM              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                             | OCRnA  | TOP                   | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                                            | ICRn   | Immediate             | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                                     | -      | -                     | -                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                                       | ICRn   | BOTTOM                | ТОР                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                                       | OCRnA  | BOTTOM                | ТОР                 |

#### Mechatronics and Microcontrollers

# 16-bites Timer/Counter VI.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### Clock Select Bits

| CSn2 | CSn1 | CSn0 | Description                                            |

|------|------|------|--------------------------------------------------------|

| 0    | 0    | 0    | No clock source. (Timer/Counter stopped)               |

| 0    | 0    | 1    | clk <sub>I/O</sub> /1 (No prescaling                   |

| 0    | 1    | 0    | clk <sub>l/O</sub> /8 (From prescaler)                 |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)               |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)              |

| 1    | 1    | 0    | External clock source on Tn pin. Clock on falling edge |

| 1    | 1    | 1    | External clock source on Tn pin. Clock on rising edge  |

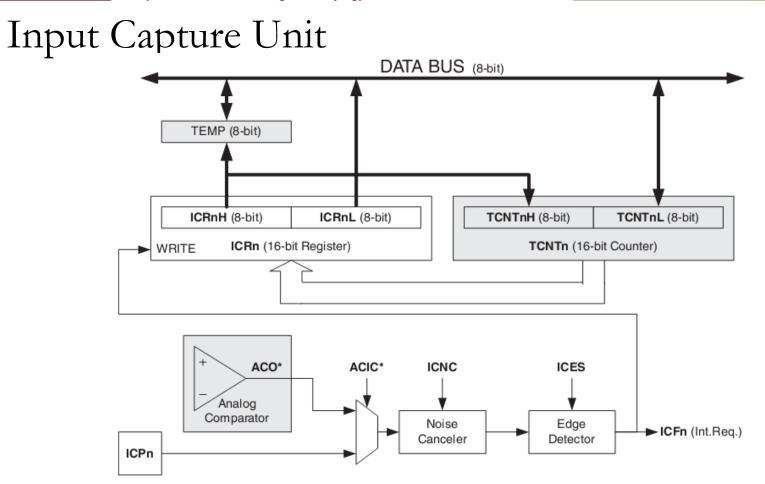

#### • Input Capture Noise Canceler (ICNCn):

• The noise canceler improves noise immunity by using a simple digital filtering scheme. The noise canceler input is monitored over four samples, and all four must be equal for changing the output that in turn is used by the edge detector.

## 16-bit Timer/Counter VII.

- Input Capture Edge Select (ICESn):

- This bit selects which edge on the Input Capture Pin (ICPn) that is used to trigger a capture event. When the ICESn bit is written to zero, a falling (negative) edge is used as trigger, and when the ICESn bit is written to one, a rising (positive) edge will trigger the capture.

- Input Capture Register (ICRnH, ICRnL):

- The Input Capture is updated with the counter (TCNTn) value each time an event occurs on the ICPn pin (or optionally on the Analog Comparator Output for Timer/Counter1).

# 16-bit Timer/Counter VIII.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### • (Extended) Timer/Counter Interrupt Mask Register (ETIMSK/TIMSK)

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1      | 0      | _      |

|---------------|-------|-------|--------|--------|--------|-------|--------|--------|--------|

|               | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0  | TOIE0  | TIMSK  |

| Read/Write    | R/W   | R/W   | R/W    | R/W    | R/W    | R/W   | R/W    | R/W    |        |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0      | 0      |        |

| Bit           | 7     | 6     | 5      | 4      | 3      | 2     | 1      | 0      |        |

|               | -     | -     | TICIE3 | OCIE3A | OCIE3B | TOIE3 | OCIE3C | OCIE1C | ETIMSK |

| Read/Write    | R     | R     | R/W    | R/W    | R/W    | R/W   | R/W    | R/W    |        |

| Initial Value | 0     | 0     | 0      | 0      | 0      | 0     | 0      | 0      |        |

- Input Capture Interrupt Enable

- Timer 1 and 3 (TICIEn)

- Output Compare Match Interrupt Enable

- 0, 1A, 1B, 1C, 2, 3A, 3B, 3C (OCIEnx)

- Timer/Counter Overflow Interrupt Enable

- Timer 0, 1, 2 and 3 (TOIEn)

# 16-bit Timer/Counter VIII.

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### • (Extended) Timer/Counter Interrupt Flag Register (ETIFR/TIFR)

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1     | 0     | _     |

|---------------|------|------|------|-------|-------|------|-------|-------|-------|

|               | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0  | TOV0  | TIFR  |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W   | R/W   | -     |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0     | 0     |       |

| Bit           | 7    | 6    | 5    | 4     | 3     | 2    | 1     | 0     |       |

|               | -    | -    | ICF3 | OCF3A | OCF3B | TOV3 | OCF3C | OCF1C | ETIFR |

| Read/Write    | R/W  | R/W  | R/W  | R/W   | R/W   | R/W  | R/W   | R/W   |       |

| Initial Value | 0    | 0    | 0    | 0     | 0     | 0    | 0     | 0     |       |

- Input Capture Flag

- Timer 1 and 3 (ICFn)

- Output Compare Match Flag

- 0, 1A, 1B, 1C, 2, 3A, 3B, 3C (OCFnx)

- Timer/Counter Overflow Flag

- Timer 0, 1, 2 and 3 (TOVn)

#### The End

Budapesti Műszaki és Gazdaságtudományi Egyetem Közlekedésautomatikai Tanszék

#### Thank you for your attention!