# REALIZATION OF BINARY OPERATIONS

Lecture 6.

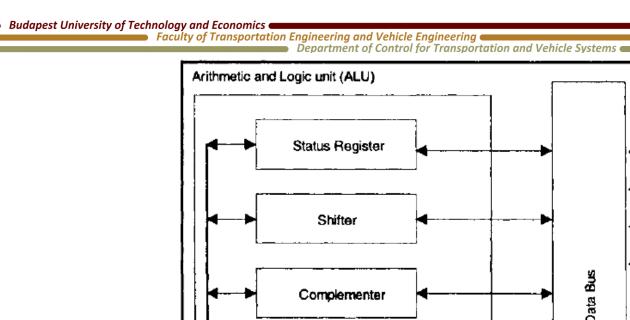

# ALU

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

- Binary operations are realized in the ALU, that can be structured in:

- serial form:

- the operations are performed bitwise, from the lowest local value toward to the higher local value,

- parallel form:

- all the operations are performed in one step in every local values,

- mixed form:

- generally used.

- Every type of artithmetic operations can be realized by addition:

- substraction,

- multiplication,

- division.

**ALU**

source: M. Rafiquzzaman, Fundamentals of Digital Logic and Microcomputer Design, 5th Edition

• ALU:

148

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

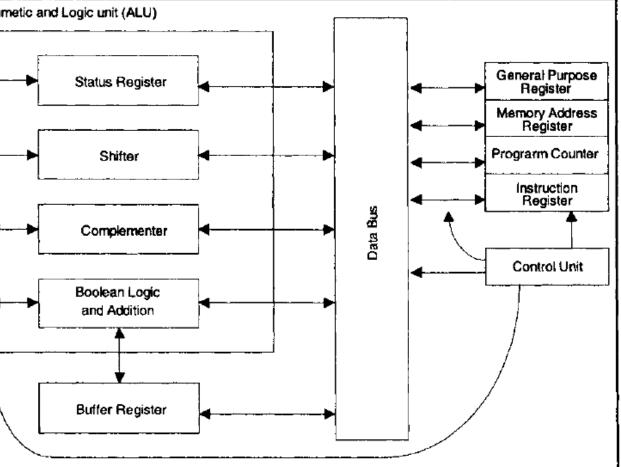

Due to the importance of the addition, the time required to add numbers plays an important role in determining the speed of the ALU,

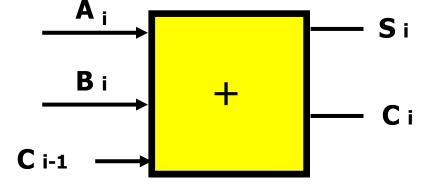

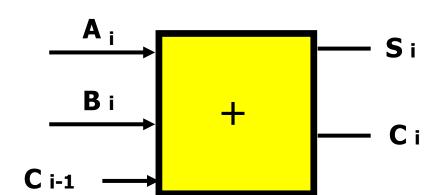

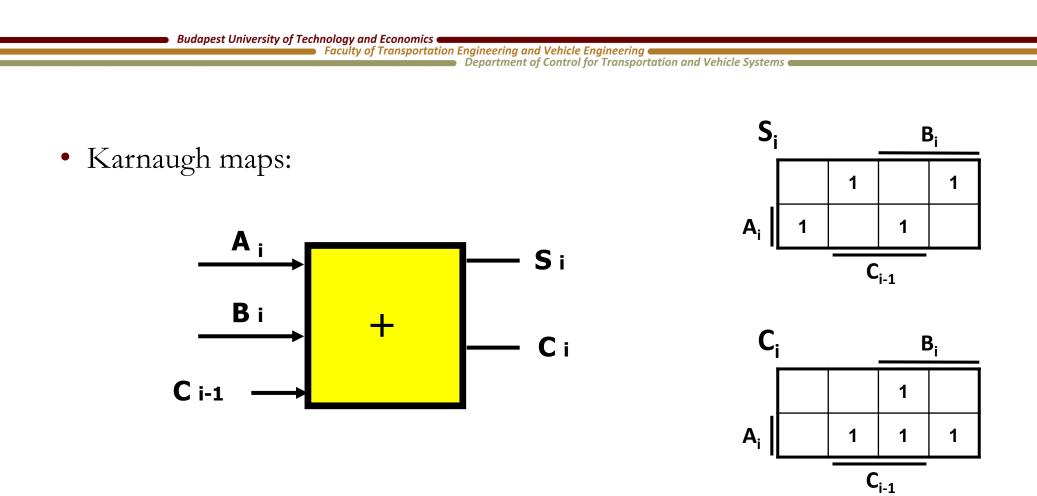

• Main types of the 1-bit adders:

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

- full adder: adds binary numbers and accounts for values carried in as well as out,

- a one-bit full adder adds three one-bit numbers, where A<sub>i</sub> and B<sub>i</sub> are the operands and C<sub>i-1</sub> is a bit carried in form the previous less-significant stage,

- a full adder is usually a component of adders, which adds 8, 16, 32, 64, etc bits binary numbers.

| Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering |                |                |                  |                |                |

|---------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|----------------|----------------|

| Department of Control for Transportation and Vo                                                               | ehicle Systems | B <sub>i</sub> | C <sub>i-1</sub> | S <sub>i</sub> | C <sub>i</sub> |

| h table of a one-bit full-adder:                                                                              | 0              | 0              | 0                | 0              | 0              |

| _                                                                                                             | 0              | 0              | 1                | 1              | 0              |

| $A_i \rightarrow A_i$ Si                                                                                      | 0              | 1              | 0                | 1              | 0              |

|                                                                                                               | 0              | 1              | 1                | 0              | 1              |

| —— C i                                                                                                        | 1              | 0              | 0                | 1              | 0              |

| C i-1 →                                                                                                       | 1              | 0              | 1                | 0              | 1              |

|                                                                                                               | 1              | 1              | 0                | 0              | 1              |

|                                                                                                               | 1              | 1              | 1                | 1              | 1              |

18/10/2018

Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

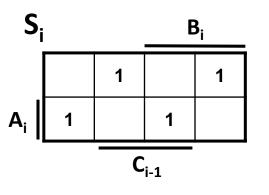

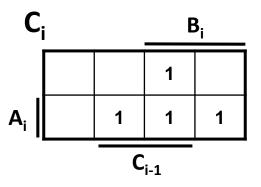

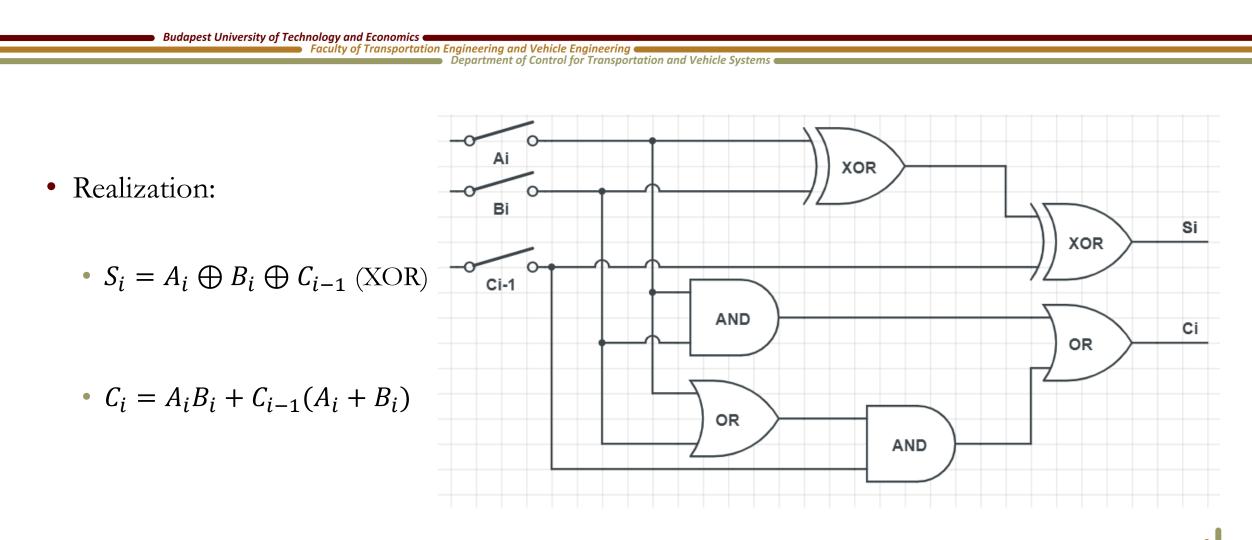

- Logical functions:

- $S_i = A_i \bigoplus B_i \bigoplus C_{i-1}$  (XOR)

•  $C_i = A_i B_i + C_{i-1} (A_i + B_i)$

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

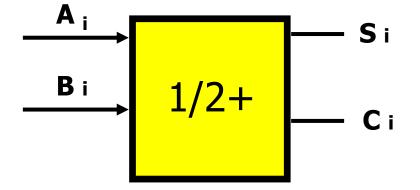

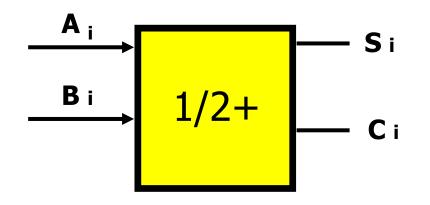

• If we add two bits:

- full adder: adds two single binary digits,

- a one-bit half-full adder adds two one-bit numbers, where A<sub>i</sub> and B<sub>i</sub> are the operands,

- it has two outputs, where the carry represents an overflow in to the next digit.

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

• Thruth table of a one-bit half-adder:

| A <sub>i</sub> | B <sub>i</sub> | S <sub>i</sub> | C <sub>i</sub> |

|----------------|----------------|----------------|----------------|

| 0              | 0              | 0              | 0              |

| 0              | 1              | 1              | 0              |

| 1              | 0              | 1              | 0              |

| 1              | 1              | 0              | 1              |

18/10/2018

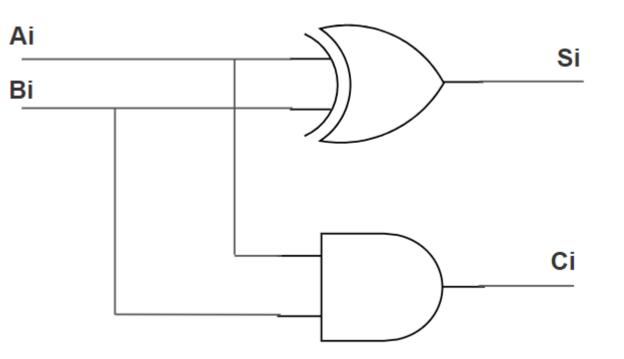

- Logical functions and realization:

- $S_i = A_i \bigoplus B_i$  (XOR)

•  $C_i = A_i B_i$

18/10/2018

Budapest University of Technology and Economics

Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

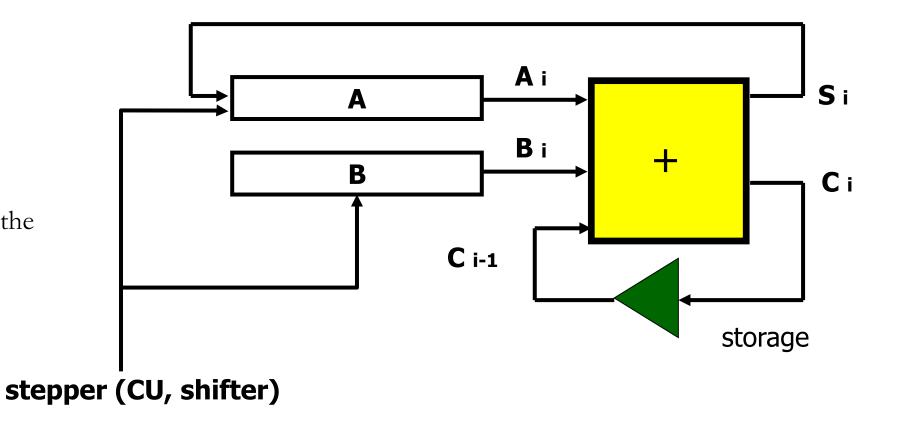

- Complex Adders:

- to add more digits,

- Serial Adder:

- the result will be in the operand A,

- it is slow.

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

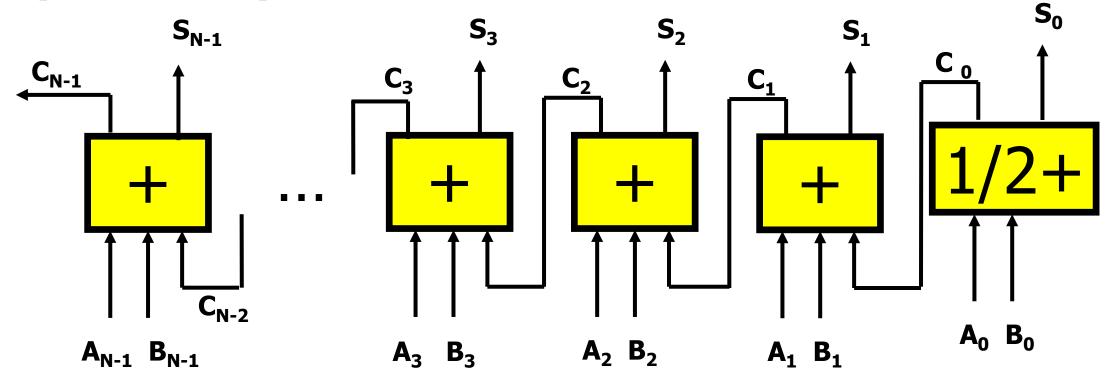

- Complex Adders:

- to add more digits,

- Riple-Carry Adder (paralell adder):

- to add N-bits,

- in this case, the adder is simple, that allows fast design time,

- the ripple-carry adder is relative slow, because each full-adder must wait for the carry bit, calculated from the previous adder, this is called the gate-daley (Δt),

- if the gate delay of a full-adder is  $3^*\Delta t$ , the result will be correct in time:  $n^* \Delta t$ , e.g the total gate delay in a case of addition of two 32 bits number:  $31^*3^* \Delta t$  (full adders) +  $1^* \Delta t$  (half-adder), the total delay=94\*  $\Delta t$

- if this time is not acceptable, it must to accelerate the addition

Budapest University of Technology and Economics

Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

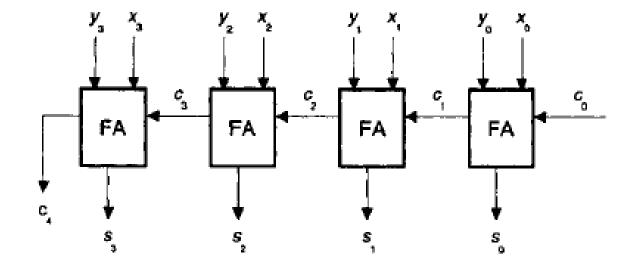

• Riple-Carry Adder (paralell adder):

Budapest University of Technology and Economics

Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

- Riple-Carry Adder (paralell adder):

- it is possible to build smaller units 4-bit Riple-Carry Adder (or carry-prpagated adder, CPA) -, because the carry is propagated serially through each full adder.

source: M. Rafiquzzaman, Fundamentals of Digital Logic and Microcomputer Design, 5th Edition

Realization of Arithmetic Operations

Budapest University of Technology and Economics Faculty of Transportation Engineering a

Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

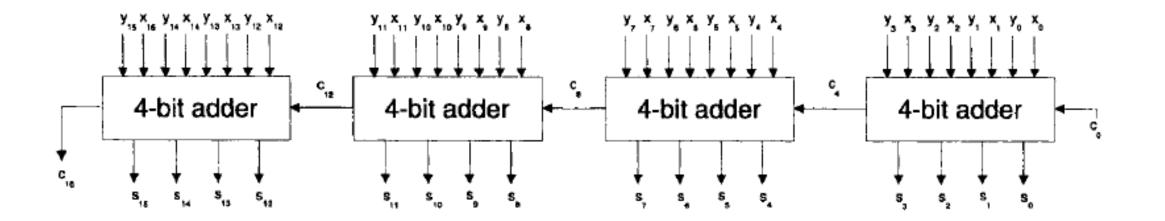

- Riple-Carry Adder (paralell adder):

- 16-bits CPA:

source: M. Rafiquzzaman, Fundamentals of Digital Logic and Microcomputer Design, 5th Edition

Realization of Arithmetic Operations

Budapest University of Technology and Economics

Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

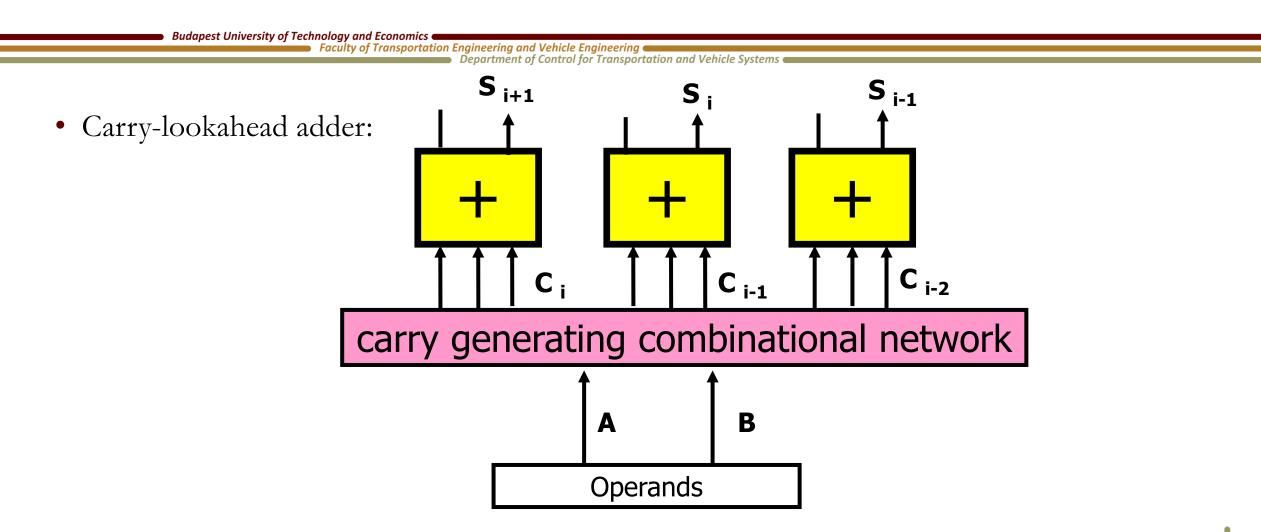

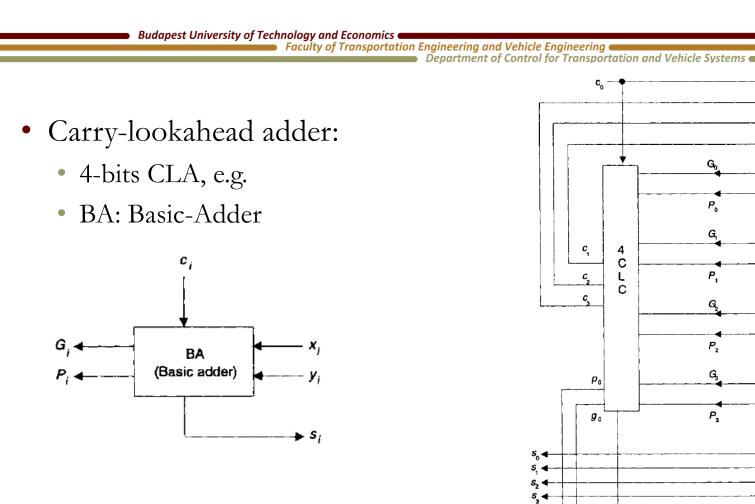

- Carry-lookahead adder:

- Idea: it is needed to determine the carry before the addition

- carry-look ahead logic uses the concept of generating and propagating carries,

- in the case of binary addition, A+B generates carry, if, and only if both A and B are 1.

- G(A,B)=A\*B

- the addition of two 1-digit inputs A and B is said to be propagate, if the addition will carry whenever there is an input carry,

- in the case of binary addition, A+B propagates a carry, if and only if at least one of A or B is 1

- P(A,B)=A+B

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

- Recursive Transfer Training method:

- $C_i = G_i + (P_i * C_{i-1})$

- $C_0 = G_0 = A_0 B_0$

- $C_1 = G_1 + P_1 C_0 = A_1 B_1 + (A_1 + B_1) A_0 B_0$

- $C_2 = G_2 + P_2 C_1 = A_2 B_2 + (A_2 + B_2)[A_1 B_1 + (A_1 + B_1)A_0 B_0] =$

- $= A_2B_2 + (A_2 + B_2)(A_1B_1 + A_0A_1B_0 + A_0B_0B_1) =$

- =  $A_2B_2 + A_1A_2B_1 + A_0A_1A_2B_0 + A_0A_2B_0B_1 + A_1B_1B_2 + A_0A_1B_0B_2 + A_0B_0B_1B_2$

- ...

- It means a complicated 2-levels combinational logical network, and contains the gate delays

- e.g. a standard 16 bit adder would take 46 gate delays, with this method it is just 5 (2+3) gate delays

source: M. Rafiquzzaman, Fundamentals of Digital Logic and Microcomputer Design, 5th Edition

· X

Y<sub>0</sub>

x,

У,

х,

У,

BA

BA

BA

BA

\_\_\_\_\_

$c_1 \leftarrow g_0 \leftarrow g_0 \leftarrow p_0 \leftarrow g_0 \leftarrow g_0$

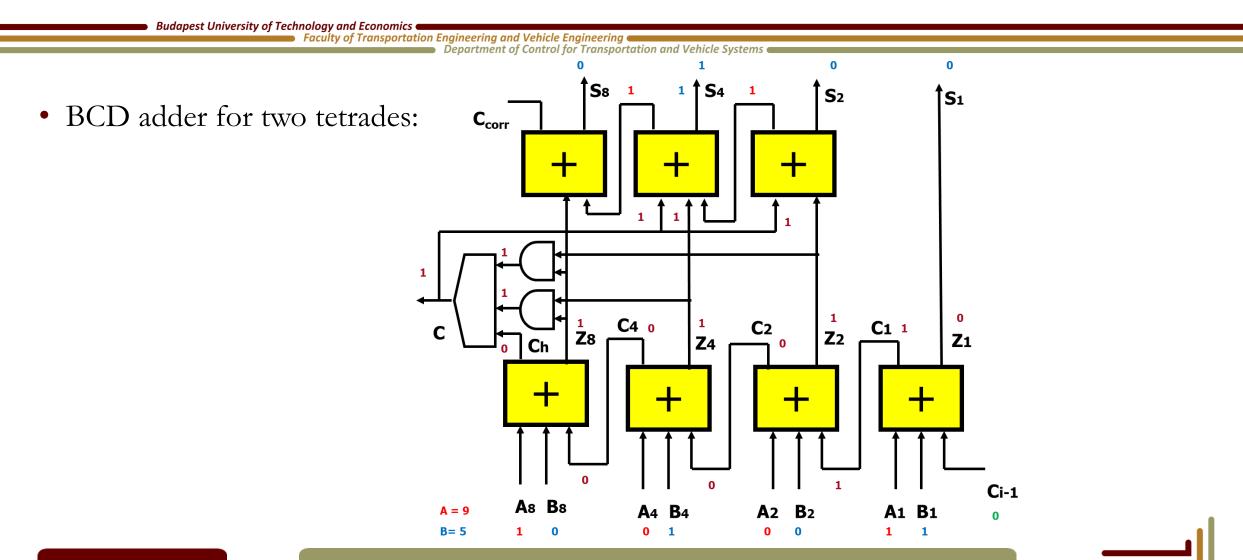

| Budapest University of Technology and Economics       Wrong Economics       Begartment of Control for Transportation and Vehicle Systems         • BCD Adder:       • Truth Table (see earlier):       0       0000       0000         • Truth Table (see earlier):       1       0001       0001       0001         • We have to create an addition       4       0100       0100       No DA       Not necessary                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>BCD Adder:         <ul> <li>Truth Table (see earlier):</li> <li>Wrong Res Z<sub>8</sub>Z<sub>4</sub>Z<sub>2</sub>Z<sub>1</sub></li> <li>S<sub>8</sub>S<sub>4</sub>S<sub>2</sub>S<sub>1</sub></li> <li>DA correction</li> </ul> </li> <li>10001 0000         <ul> <li>00001</li> <li>0001</li> <li>0001</li> <li>0001</li> <li>0010</li> <li>0010</li> <li>0011</li> <li>0011</li> <li>0010</li> <li>No DA</li> </ul> </li> </ul> |

| • Truth Table (see earlier):       0       0000       0000         1       0001       0001         2       0010       0010         3       0011       0011         • we have to create an addition       4       0100       0100                                                                                                                                                                                                          |

| 200100010300110011401000100No DANot necessary                                                                                                                                                                                                                                                                                                                                                                                             |

| • we have to create an addition 4 0100 0100 No DA Not necessary                                                                                                                                                                                                                                                                                                                                                                           |

| • we have to create an addition 4 0100 0100 No DA Not necessary                                                                                                                                                                                                                                                                                                                                                                           |

| • We have to create an addition No DA Not necessary                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| if the result is beetween 6 0110 0110                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9 <res<16, 0111="" 0111<="" 7="" td=""></res<16,>                                                                                                                                                                                                                                                                                                                                                                                         |

| 8 1000 1000                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9 1001 1001                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • if the result is bigger then $10$ 1010 0000<br>11 1011 0001                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15, it is needed to create the 12 1100 0010 No DA, it has                                                                                                                                                                                                                                                                                                                                                                                 |

| decimal adjust 13 1101 0011 to generate it +6                                                                                                                                                                                                                                                                                                                                                                                             |

| 14 1110 0100 (+0110)                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15 1111 0101                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| • $C = Z_4 * Z_8 + Z_2 * Z_8 + C_h$ 17 (1)0001 0111 it generates                                                                                                                                                                                                                                                                                                                                                                          |

Realization of Arithmetic Operations

1000

167

(1)0010

18

18/10/2018

Realization of Arithmetic Operations

168

Budapest University of Technology and Economics Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

- Multiplication by 2:

- or with  $2^x$

- Division by 2:

- or with  $2^x$

18/10/2018

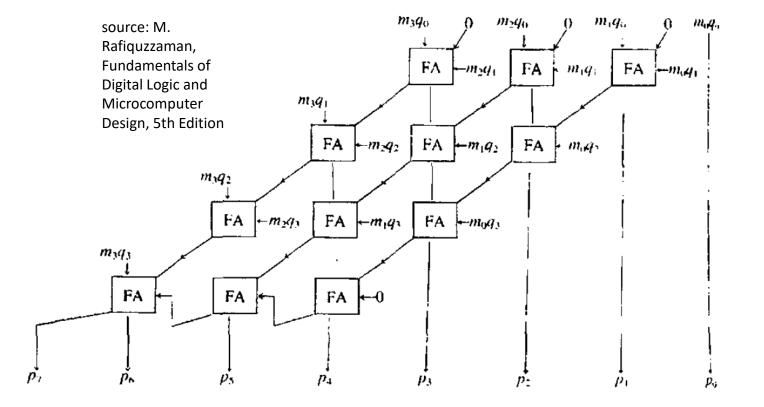

# Multiplication

Budapest University of Technology and Economics

Faculty of Transportation Engineering and Vehicle Engineering Department of Control for Transportation and Vehicle Systems

Multiplication by leftforward shihting, 4x4 Array Multiplier:

### ALU

Budapest University of Technology and Economics

Faculty of Transportation Engineering and Vehicle Engineering

Department of Control for Transportation and Vehicle Systems

- <u>https://www.youtube.com/watch?v=K79wfflmLNo</u>

- <u>https://www.youtube.com/watch?v=1I5ZMmrOfnA</u>

- <u>https://www.youtube.com/watch?v=fpnE6UAfbtU</u>

- <u>https://www.youtube.com/watch?v=FZGugFqdr60</u>

## End of Lecture 6.

Thank you for your attention!